# **RT9114B Audio Evaluation Board**

### **Purpose**

The RT9114B is a high efficiency, I2S-input, stereo channel audio power amplifier which delivering 2x18W into 8 ohm BTL speaker loads. It can deliver over 90% power efficiency and eliminate the need for heat-sink. This document explains the function and usage of the RT9114BGQV evaluation board (EVB), and provides information for power-up operation, and the modification of the evaluation board and the circuit, to be suitable for individual requirements.

# **Table of Contents**

| Purpose                                      | 1 |

|----------------------------------------------|---|

| ntroduction                                  | 2 |

| Key Performance Summary Table                | 2 |

| Bench Test Setup Conditions                  | 3 |

| Schematic, Bill of Materials & Board Layout  | 5 |

| More Information                             | 7 |

| mportant Notice for Richtek Evaluation Board | - |

### Introduction

#### General Product Information

The RT9114B is an I<sup>2</sup>S device receiving all clocks from external sources. It can support both master and slave mode with wide input sampling rate from 8kHz to 96kHz. The RT9114B operates with a PWM switching frequency of 352kHz or 384kHz, depending on the input sampling rate. A fully programmable data path routes these channels to the internal speaker drivers.

The RT9114B features three band DRC and flexible multi-band biquads for anti-clipping, power limiting, and speaker equalization.

#### **Product Feature**

- 8V to 2.4V Input Voltage Range

- 2x18W at 10% THD+N into 8Ω BTL at 18V

- 2x9W at 10% THD+N into 8Ω BTL at 12V

- Support Stereo Channels Output

- · Sampling Frequency from 8kHz to 96kHz

- Built-in Anti-Pop Function for BTL BD Modulations

- > 24 Programmable Biquads for Speaker Equalization

- Programmable Coefficients for DRC Filters

- Supporting Multi-Compression Ratios

- . Built-in DC Blocking Filters

- Protection Features : UVLO, OVP, OCP, DCP and OTP

- VQFN-28L Thermally-Enhanced Package

### Key Performance Summary Table

| Key Features                                               | Evaluation Board Number : RT9114B_Q4X5_28L_V0 |

|------------------------------------------------------------|-----------------------------------------------|

| Default Input Voltage                                      | 12V                                           |

| RMS Output Power, THD + N = 10%, $8\Omega$ Load, (BTL)     | 9W                                            |

| RMS Output Power, THD + N = 1%, $8\Omega$ Load, (BTL)      | 6.5W                                          |

| Total Harmonic Distortion+Noise,<br>PO = 1W, 8ΩLoad, (BTL) | 0.03%                                         |

| OCP Threshold                                              | 6.3A                                          |

### **Bench Test Setup Conditions**

### Headers Description and Placement

Carefully inspect all the components used in the EVB according to the following Bill of Materials table, and then make sure all the components are undamaged and correctly installed. If there is any missing or damaged component, which may have occurred during transportation, please contact our distributors or e-mail us at <a href="mailto:evb\_service@richtek.com">evb\_service@richtek.com</a>.

#### **Test Points**

The EVB is provided with the test points and pin names listed in the table below.

| Test point /<br>Pin name | Signal                                       | Comment (expected waveforms or voltage levels on test points) |  |  |

|--------------------------|----------------------------------------------|---------------------------------------------------------------|--|--|

| PVDD                     | Input Voltage                                | Power input. Support 8V to 26.4V input voltage.               |  |  |

| 3.3V Enable Test Point   |                                              | Power input. Support 3V to 3.6V input voltage.                |  |  |

| PVSS                     | Ground                                       | Ground.                                                       |  |  |

| OUT_PL,<br>OUT_NL        | Speaker Differential<br>Output Left Channel  | Connect speaker or dumy load.                                 |  |  |

| OUT_NR,<br>OUT_PR        | Speaker Differential<br>Output Right Channel | Connect speaker or dumy load.                                 |  |  |

| SCL, SDA                 | I <sup>2</sup> C Signal                      | Connect I <sup>2</sup> C signal.                              |  |  |

| BCK, LRCK,<br>DOUT       | I <sup>2</sup> S Signal                      | Connect I <sup>2</sup> S signal.                              |  |  |

| FAULT                    | FAULT Behaviour                              | It will pull low when protection behavior is happened.        |  |  |

#### Power-up & Measurement Procedure

- 1. The 1X3 Header (JP4) is the RESETB. (JP4 setting: Short PIN1;2 = Disable, Short PIN2;3 = Enable).

- 2. The 1X3 Header (JP7) is the PWDNB. (JP7 setting : Short PIN1;2 = Disable, Short PIN2;3 = Enable).

- 3. The 1X3 Header (JP8) is the FAULTB.

- 4. The 1X3 Header (JP9) is the A\_SEL. (JP9 setting : Short PIN1;2 = 1A, Short PIN2;3 = 1B) and see A\_SEL setting as Table 1.

| A_SEL | Addr |

|-------|------|

| 0     | 1A   |

| 1     | 1B   |

Table 1. A\_SEL Setting

- 5. Apply  $8\Omega$  speakers to the speaker connection (GP5 (OUT\_PL), GP6 (OUT\_NL), GP7 (OUT\_NR), and GP8 (OUT\_PR).

- 6. Apply I<sup>2</sup>S digital audio signals to JP2 (PIN2 = MCLK (Option), PIN4 = LRCK, PIN6 = SCLK, PIN8 = SDI, PIN10 = SDO).

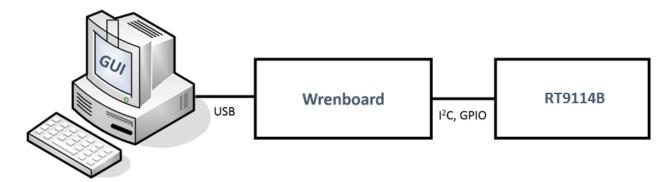

- 7. Connect the GND, SCL, SDA wires from Wrenboard to J2 (PIN1 = PVSS, PIN3 = SCL, PIN5 = SDA). Then connect the Richtek Wrenboard to the PC. Apply Wrenboard with 3.3V configuration and please refer to Wrenboard User Manual for the installation and operation. Please note you'll need the RICHTEK Wrenboard I<sup>2</sup>C interface for controlling the RT9114B EVB.

- 8. Apply an input power supply (8V < PVCC < 26.4V) to the PVDD and PVSS (GND) pins respectively.

- 9. Apply an input power supply (3.3V) to the DVDD and PVSS (GND) pins respectively.

- 10. Turn on the power.

- 11. Apply the initial sequence. Please refer to RT9114B GUI User Manual to operate the GUI tool.

Figure 1. The connection of RT9114B, Wrenboard, and PC

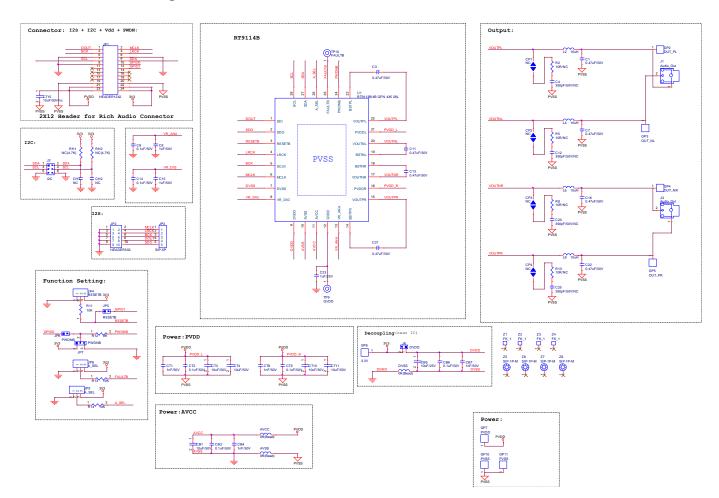

# Schematic, Bill of Materials & Board Layout

# **EVB Schematic Diagram**

#### Bill of Materials

| Reference                              | Qty | Part Number         | Description                   | Package      | Manufacturer   |  |  |

|----------------------------------------|-----|---------------------|-------------------------------|--------------|----------------|--|--|

| U1                                     | 1   | RT9114BGQV          | 15W Stereo Audio<br>Amplifier | VQFN-28L 4x5 | Richtek        |  |  |

| C1, C3, C7, C11,<br>C13, C16, C21, C22 | 8   | C1608X7R1H474K080AC | 470nF/50V                     | 0603         | TDK            |  |  |

| C4, C12, C20, C25                      | 4   | 0603B391K500CT      | 390pF/50V                     | 0603         | WALSIN         |  |  |

| C8, C14, CB3, CB6,<br>CT2              | 5   | C1608X7R1H104K080AA | 100nF/50V                     | 0603         | TDK            |  |  |

| C9, C15, C23                           | 3   | C1608X5R1E105K080AC | 1μF/25V                       | 0603         | TDK            |  |  |

| CB1, CB5, CT3,<br>CT4, CT10, CT11      | 6   |                     | 10μF/50V                      | 1210         | muRata         |  |  |

| CB4, CB7, CT1,<br>CT8                  | 4   | 0603B102K500CT      | 1nF/50V                       | 0603         | WALSIN         |  |  |

| CT9                                    | 1   | 0603N101J500CT      | 100pF/50V                     | 0603         | WALSIN         |  |  |

| CT15                                   | 1   | C3216X5R1H106K160AB | 10μF/50V                      | 1206         | TDK            |  |  |

| L2, L4, L6, L8                         | 4   | NR8040T100M         | 10μH                          |              | TAIYO<br>YUDEN |  |  |

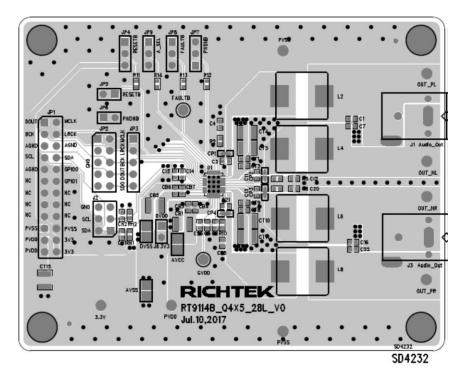

# PCB Layout

Top View

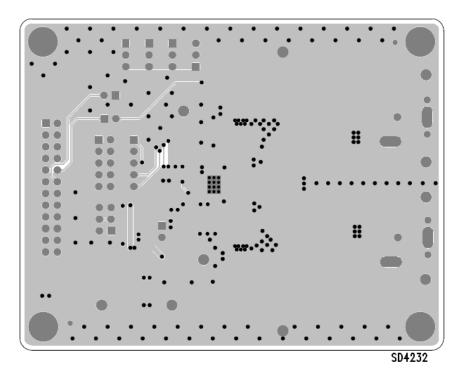

**Bottom View**

### **More Information**

For more information, please find the related datasheet or application notes from Richtek website <a href="http://www.richtek.com">http://www.richtek.com</a>.

# Important Notice for Richtek Evaluation Board

THIS DOCUMENT IS FOR REFERENCE ONLY, NOTHING CONTAINED IN THIS DOCUMENT SHALL BE CONSTRUED AS RICHTEK'S WARRANTY, EXPRESS OR IMPLIED, UNDER CONTRACT, TORT OR STATUTORY, WITH RESPECT TO THE PRESENTATION HEREIN. IN NO EVENT SHALL RICHTEK BE LIABLE TO BUYER OR USER FOR ANY AND ALL DAMAGES INCLUDING WITHOUT LIMITATION TO DIRECT, INDIRECT, SPECIAL, PUNITIVE OR CONSEQUENTIAL DAMAGES.